## BESTAWAILABLECCORY

Appln No. 09/517,541 Amdt. Dated March 23, 2006 Response to Office Action of February 3, 2006

2

When designing such conventional CMOS logic, one of ordinary skill in the art of CMOS circuit design would not take the possible emission of light pulses from such circuits into consideration. This is because, one of ordinary skill in the art of CMOS circuit design would not be aware of the possibility of light emission from such circuits, nor the ability to use such emission to view the data being manipulated.

Thus, it is not well known to one of ordinary skill in the art of CMOS circuit design to design pMOS and nMOS transistors to be driven such that they do not have intermediate resistance simultaneously during a change of state of the CMOS structure, to manipulate the secret data, and operating conventional CMOS inverters adjacent the non-flashing CMOS structures at the same time.

Accordingly, if the Examiner is to maintain the asserted well known statement, the Examiner is again respectfully requested to provide supporting documentary evidence under MPEP §2144.03.

## Regarding 35 USC 103(a) Rejections

Notwithstanding the above rebuttal of the Examiner's statement of what is purported to be well known in the art, it is further respectfully submitted that there is no motivation for one of ordinary skill in the art to modify the disclosed CMOS circuit of Park to obtain a nonflashing CMOS structure as claimed in the claimed invention.

This is because, the CMOS structure disclosed by Park, as illustrated in Fig. 3, is an example of an analogue CMOS circuit which, when turned on, will have continuous current flowing. This continuous current is necessary for the desired operation of the circuit as a word line generator. That is, there is no motivation to modify the disclosed circuit to be "non-flashing", e.g., driving the pMOS and nMOS transistors under non-synchronized clock signals as claimed in pending claims 9 and 10, as it relies on linear and continuous time amplification to provide a constant (while on) output voltage (see, for example, col. 4, line 18-col. 5, line 27 of Park).

Thus, it is respectfully submitted that the subject matter of pending claims 1-10 is not taught or suggested by Park either taken alone or in combination with what the Examiner purports as being well known.

It is respectfully submitted that all of the Examiner's rejections have been traversed. Accordingly, it is submitted that the present application is in condition for allowance and reconsideration of the present application is respectfully requested.

Very respectfully,

Applicants:

KIA SILVERBROOK

SIMON ROBERT WALMSLEY

C/o:

Silverbrook Research Pty Ltd 393 Darling Street Balmain NSW 2041, Australia

Email:kia.silverbrook@silverbrookresearch.comTelephone:+612 9818 6633Facsimile:+61 2 9555 7762

3

M. C. Varley,

Sponsoring Editor

Hugh Crawford, Richard Hannus, Cover Designer Maureen Langer,

Manufacturing Supervisor Mary Crittendon, Project Supervisor Text Designer Elydia P. Siegel, Production Editor

This book is in the Addison-Wesley VLSI Systems Series Lynn Conway and Charles Seitz, Consulting Editors

Library of Congress Cataloging in Publication Data Weste, Neil.

Principles of CMOS VLSI design.

Bibliography: p.

Includes index.

1. Integrated circuits-Very large scale integration -Design and construction. 2. Metaloxide semiconductors, Complementary. I. Eshraghian, Kamran. II. Title. III. Title: Principles of C.M.O.S. V.L.S.I. design. TK7874.W46 1985 621.381'73 84–16738 ISBN 0-201-08222-5

### Reprinted with corrections October, 1985

Copyright © 1985 by AT&T Bell Laboratories, Incorporated, and Kamran Eshraghian

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

EFGHIJ-HA-89876

۶d

in ite

ot

he

ar to

.8)

·bγ

:.9)

. `he hat ion ent

### THE COMPLEMENTARY CMOS INVERTER - DC CHARACTERISTICS 2.3

source, the current being almost independent of  $V_{ds}$ . This may be verified from Eq. (2.2c) since

1 -

$$\frac{dI_{ds}}{dV_{ds}} = \frac{d\left(\frac{\beta}{2}(V_{gs} - V_t)^2\right)}{dV_{ds}} = 0.$$

(2.10)

The transconductance  $g_m$  expresses the relationship between output current  $I_{ds}$  and the input voltage  $V_{gs}$ , and is defined by

$$g_m = \frac{\partial I_{ds}}{\partial V_{gs}} \bigg|_{V_{ds}=constant}$$

(2.11)

It is used to measure the gain of an MOS device. In the linear region,  $g_m$  is given by

$$g_{m(linear)} = \beta V_{ds}, \qquad (2.12)$$

and in the saturation region by

$$g_{m (sat)} = \beta (V_{gs} - V_t).$$

(2.13)

For example, the value of transconductance for an n-type transistor in the linear region is

$$g_{m_n} = \left(\frac{\mu_n \varepsilon}{t_{ox}}\right) \left(\frac{W_n}{L_n}\right) V_{ds}.$$

(2.14)

Since transconductance must have a positive value, absolute values are used for voltages applied to p-type devices.

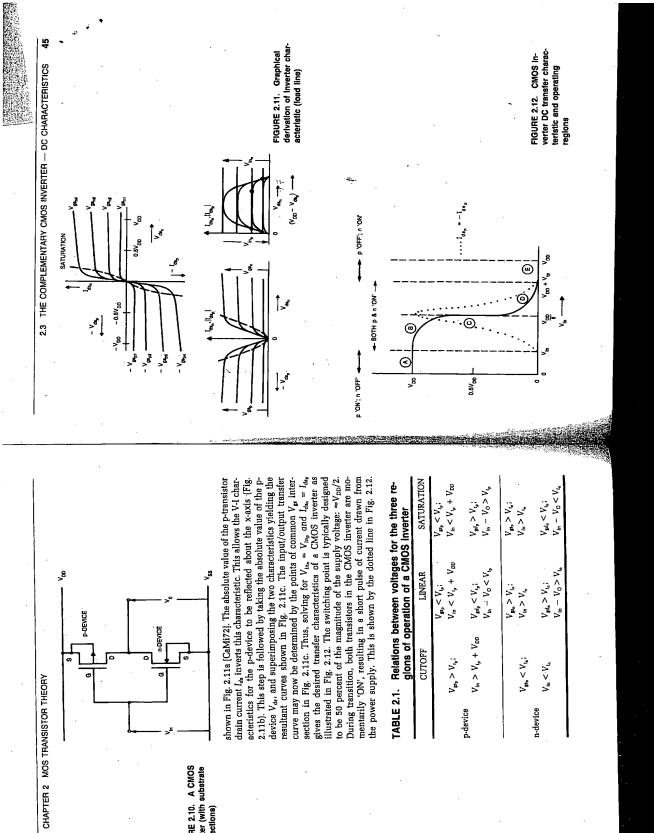

### 2.3 The complementary CMOS inverter ----DC characteristics

A complementary CMOS inverter is realized by the series connection of a p- and n-device, as shown in Fig. 2.10. In order to derive the DC transfer characteristics for the inverter (output voltage  $V_0$  as a function of  $V_{in}$ ), we start with Table 2.1, which outlines various regions of operation for the n- and p-transistors. In this table,  $V_{t_n}$ is the threshold voltage of the n-channel device, and  $V_{t_p}$  is the threshold voltage of the p-channel device. The objective is to find the variation in output voltage ( $V_O$ ) for changes in the input voltage  $(V_{in}).$

We commence with the graphical representation of the simple algebraic equations described by Eq. (2.2) for the two transistors 43

44

FIGURE 2.10. A CMOS

inverter (with substrate connections)

# This Page is Inserted by IFW Indexing and Scanning Operations and is not part of the Official Record

## **BEST AVAILABLE IMAGES**

Defective images within this document are accurate representations of the original documents submitted by the applicant.

Defects in the images include but are not limited to the items checked:

**BLACK BORDERS**

□ IMAGE CUT OFF AT TOP, BOTTOM OR SIDES

□ FADED TEXT OR DRAWING

□ BLURRED OR ILLEGIBLE TEXT OR DRAWING

□ SKEWED/SLANTED IMAGES

$\Box$  COLOR OR BLACK AND WHITE PHOTOGRAPHS

**GRAY SCALE DOCUMENTS**

**D** LINES OR MARKS ON ORIGINAL DOCUMENT

□ REFERENCE(S) OR EXHIBIT(S) SUBMITTED ARE POOR QUALITY

OTHER:

## IMAGES ARE BEST AVAILABLE COPY.

As rescanning these documents will not correct the image problems checked, please do not report these problems to the IFW Image Problem Mailbox.